## ACS APPLIED MATERIALS & INTERFACES

# Pulsed Transfer Etching of PS–PDMS Block Copolymers Self-Assembled in 193 nm Lithography Stacks

Cécile Girardot, Sophie Böhme, Sophie Archambault, Mathieu Salaün, Eddy Latu-Romain, Gilles Cunge, Olivier Joubert, and Marc Zelsmann\*

Université Grenoble Alpes, Laboratoire des Technologies de la Microélectronique , F-38000 Grenoble, France

Centre National de la Recherche Scientifique, LTM, F-38000 Grenoble, France

CEA, LETI, MINATEC Campus, F-38054 Grenoble, France

**ABSTRACT:** This work presents the graphoepitaxy of high- $\chi$  block copolymers (BCP) in standard industry-like lithography stacks and their transfer into the silicon substrate The process includes conventional 193 nm photolithography, directed self-assembly of polystyrene-block-polydimethylsiloxane (PS-*b*-PDMS) and pulsed plasma etching to transfer the obtained features into the substrate. PS-*b*-PDMS has a high Flory–Huggins interaction parameter (high- $\chi$ ) and is capable of achieving sub-10 nm feature sizes. The photolithography stack is fabricated on 300 mm diameter silicon wafers and is composed of three layers: spin-on-carbon (SoC), silicon-containing anti-reflective coating (SiARC) and 193 nm photolithography resist. Sixty-nanometer-deep trenches are first

patterned by plasma etching in the SiARC/SoC stack using the resist mask. The PS-*b*-PDMS is then spread on the substrate surface. Directed self-assembly (DSA) of the BCP is induced by a solvent vapor annealing process and PDMS cylinders parallel to the substrate surface are obtained. The surface chemistry based on SoC permits an efficient etching process into the underlying silicon substrate. The etching process is performed under dedicated pulsed plasma etching conditions. Fifteen nanometer half-pitch dense line/space features are obtained with a height up to 90 nm.

KEYWORDS: directed self-assembly (DSA), PS-b-PDMS, graphoepitaxy, plasma etching, silicon nanostructures

### I. INTRODUCTION

Because of the increased capabilities of electronic devices and their decreasing critical dimensions, the demand for nanoscale fabrication methods has expanded in recent years. As alternatives to standard UV projection photolithography, sophisticated top-down approaches like e-beam,<sup>1</sup> EUV or Xray<sup>2</sup> lithography have shown promising results in terms of improved resolution but at high cost and or low throughput. In parallel, more cost-effective high-resolution fabrication methods have been developed like nanoimprint lithography<sup>3,4</sup> or block copolymer (BCP) self-assembly.<sup>5</sup> The combination of this latter bottom-up approach with a cost-effective top-down technique is a productive way to obtain high resolution features at a reasonable cost.<sup>6</sup> Indeed, directed self-assembly (DSA) of BCP produces thin films with various nanosized patterns<sup>6-10</sup> and feature sizes smaller than 10 nm.<sup>10-12</sup> It was consequently introduced in the International Technology Roadmap for Semiconductors (ITRS) in order to complement advanced optical lithography techniques by increasing the resolution.<sup>13</sup> In this work, we present the self-assembly of high- $\chi$  block copolymers as a complement to conventional 193 nm wavelength photolithography.

BCP consist of two (or more) immiscible polymers that are covalently bonded and undergo a phase separation when

enough energy for block movement is provided. Different morphologies (spheres, cylinders, lamellae) are then obtained, mainly depending on the volume fraction of each phase.<sup>14</sup> On planar substrates, self-assembled features are aligned in small areas not larger than a few micrometers but when deposited on topographically modified surfaces (graphoepitaxy process) lithographed patterns can guide the BCP self-assembly over long-range orders.

The Flory–Huggins parameter  $\chi$  reflects the incompatibility between the two blocks of a copolymer. The higher the  $\chi$ -value, the higher the achievable pattern resolution. Nowadays, most of the research on BCP lithography is concentrated on polystyrene-block-poly(methyl methacrylate) (PS-*b*-PMMA) because of its ease of processing. This copolymer is commercially available and can be processed quite easily by thermal annealing and integrated with existing microelectronic tools.<sup>12</sup> Nevertheless, PS-*b*-PMMA has a low Flory–Huggins parameter  $\chi$  ( $\chi$  = 0.06 at 298 K<sup>15</sup>), limiting its resolution. For this reason, high- $\chi$  BCPs like PS-*block*-polyethylene (PS-*b*-PEO), polydimethylsiloxane-block-poly-2-vinylpyridine

```

Received: July 9, 2014

Accepted: August 11, 2014

Published: August 11, 2014

```

ACS Publications © 2014 American Chemical Society

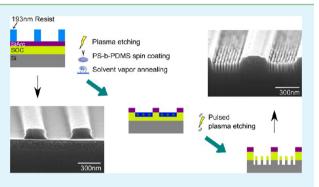

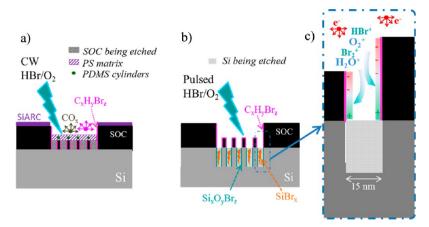

**Figure 1.** Schematic of the integration process of PS-*b*-PDMS with a standard trilayer 193 nm photolithography stack: (1) Plasma etching in the SiARC and SoC layers using the 193 nm photolithography resist mask; (2) PS-*b*-PDMS spin coating, self-assembly by SVA, and short plasma etching to reveal the oxidized PDMS nanostructures; (3) transfer etching into the remaining SoC layer and (4) into the underlying silicon substrate.

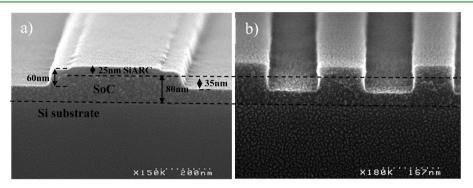

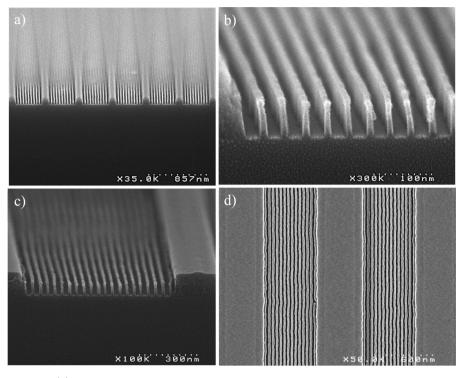

Figure 2. Cross-section SEM images of the SiARC/SoC graphoepitaxy template. (a) 500 nm and (b) 100 nm large lines.

(PDMS-*b*-P2VP), polystyrene-block-poly(styrene-*b*-lactide) (PS-*b*-PLA) or polystyrene-block-polydimethylsiloxane (PS-*b*-PDMS) are gaining more interest.<sup>12</sup> PS-*b*-PDMS shows in particular several advantages.<sup>7,11,16,17</sup> Its  $\chi$  value is 0.26 at 300 K.<sup>15</sup> This allows smaller periodicities and/or sharper interfaces (periodicity of ~10 nm). Furthermore, the PDMS block contains a high quantity of silicon, which generates a good etching contrast with the PS block and makes it a robust hard mask for further lithography processes.<sup>17</sup> More precisely, the PDMS block easily forms silicon oxide structures under oxygen plasma, whereas the PS block is degraded under the same treatment.<sup>18,19</sup>

However, because of the high incompatibility of the two blocks, thermal diffusion is not effective enough to thermally produce self-assembly in reasonable processing times. Hence, other nonstandard self-assembly methods have to be introduced.<sup>20</sup> The most common method is solvent vapor annealing (SVA) where the sample is exposed to a solvent vapor. Solvent molecules swell the BCP thin film, reducing the diffusive energy barrier and allowing the self-assembly to take place at room temperature.<sup>16</sup>

In this work, a complete process of directed self-assembly of PS–PDMS in standard spin-on-carbon (SoC)/silicon-containing anti-reflective coating (SiARC) layers and their transfer into silicon by pulsed plasma etching is developed. In the following sections, the technological steps are detailed.

In Figure 1, a schematic of the process flow is presented. First, the photolithography mask is used to etch the SiARC layer and partially the SoC layer to create the self-assembly template (step 1). Then, the cylinder forming PS-*b*-PDMS film is deposited in the trenches and self-assembled by solvent vapor annealing (step 2). Self-assembled structures are transferred into the remaining SoC layer in step 3 and finally into the silicon substrate by dedicated pulsed plasma etching processes (step 4).

#### 2. DIRECTED SELF-ASSEMBLY OF PS-B-PDMS

**2.1. Plasma Etching Reactor.** Experiments are performed in a 300 mm diameter AdvantEdge ICP (inductively coupled plasma) etch tool from Applied Materials as described in.<sup>21,22</sup> The plasma is excited inductively by a Radio Frequency (RF) power source at 13.56 MHz via two concentric RF coils (ICP coil) in order to produce a uniform ions flux. The wafer is biased independently using a second power supply capacitively coupled to the electrostatic chuck. Two modes are available in the etching tool: a continuous wave (CW) mode where the plasma is excited with constant RF power and a "pulsed" mode, in which the ICP source and the bias power supply are pulsed synchronously (via a Pulsync Applied Materials RF system). Typical pulsing frequencies are between 100 Hz and 20 kHz, with duty cycles between 10 and 90%.<sup>23,24</sup> In this work, both CW and pulsed mode are used depending on the etching step.

2.2. Etching Process for Template Preparation. The graphoepitaxy of horizontally oriented PDMS cylinders on topographically modified substrates allows the production of long-range order aligned nanostructures. The prepatterned substrate, consisting of the described SiARC/SoC layers, is obtained with plasma etching in CW mode using a conventional 193 nm wavelength photolithography mask. This mask was generated with last generation resists on 300 mm wafers, using a SOKUDO RF3 coating track interfaced with a Nikon S307E 0.85NA dry ArF scanner. All parameters used were set based on suppliers recommendations. Achieved resolution is better than 100 nm. Ar/CF<sub>4</sub>/CHF<sub>3</sub> and HBr/O<sub>2</sub> chemistries are used for SiARC and partial SoC etching, respectively. Scanning Electron Microscopy (SEM) cross-section images of obtained trenches (widths varying from 100 to 500 nm) are shown in Figure 2. The trenches consist of an approximately 25 nm thick SiARC and 35 nm thick SoC layer, leading to a total trench depth of about 60 nm. The process conditions are adjusted so that at the end of the process, no photoresist remains on the SiARC layer. However, this complete lift off of the photoresist is at the expense of layer uniformity on the

larger lines (Figure 2, left) because no etch-stop barrier layer is provided. Nevertheless, the nonuniformity of the SiARC layer was found not to be critical in the graphoepitaxy process.

2.3. PDMS Horizontal Cylinders Formation. Diblock copolymer of cylinder forming PS-b-PDMS ( $M_{PS-b-PDMS} = 45.5$ kg mol<sup>-1</sup> in which  $M_{PDMS} = 14.5$  kg mol<sup>-1</sup>), was purchased from Polymer Source, Inc. Toluene and propylene glycol monomethyl ether acetate (PGMEA) were used as solvents.

The PS-*b*-PDMS is dissolved in PGMEA (1, 1.5, and 2 wt %) and spin-coated (1000-3000 rpm) onto patterned SiARC/SoC templates. PGMEA is a common lithography solvent that provides a better wetting of the SiARC/SoC sample surfaces compared to spin-cast solutions prepared with toluene. Selfassembly is performed by solvent vapor annealing in a closed vessel with saturated toluene vapor at room temperature and atmospheric pressure for 3 h. Then, samples are taken out and exposed to dry air to evaporate the solvent. Conditions (BCP dilution, spin speed and trenches opening ratio) were adjusted to yield a polymer thickness of 30 nm into the trenches after SVA. This thickness is close to the natural self-organization period  $(L_0)$  of the used polymer  $(L_0 \approx 35 \text{ nm})$ .

To efficiently direct the alignment and facilitate the longrange ordering of horizontal cylinders along patterned trenches, both the sidewalls and the bottom of the trenches should present a preferential attraction to the major block of the copolymer. Modifying the surface chemistry of the substrate is known to have strong effects on the orientation of the PDMS cylinders.<sup>25</sup> Therefore, scanning transmission electron microscopy (STEM) imagery was performed on self-assembled PS-PDMS within SiARC/SoC trenches (Figure 3) to evaluate the

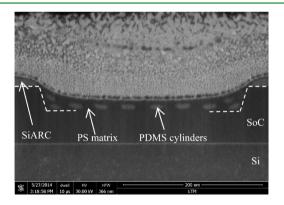

Figure 3. Dark-field STEM images of PDMS cylinders in the PSmatrix formed after SVA in SiARC/SoC trenches.

wetting behavior of PS-b-PDMS. The PDMS cylinders that can be seen in Figure 3 show an elongated form. This has already been observed elsewhere<sup>26</sup> and is due to the solvent evaporation during SVA when going from the swollen to the final dried state.<sup>20</sup> Significant strain is induced on the film during drying which can affect the dimension and shape of the nanostructures.

Due to the high chemical similarity between SoC (mostly composed of carbon) and PS, no PDMS wetting layer between the copolymer and the bottom of the trenches is found. This observation can further be confirmed by the fact that the transfer etching of the PDMS lines into the SoC layer can be carried out with a simple HBr/O<sub>2</sub> plasma (see section 3.1). A PDMS wetting layer at the interface would be oxygen resistant, and would consequently not allow such a transfer etching. This wetting behavior allows indeed the wetting of the PS block (BCP matrix) and thus in addition the rapid formation of horizontal PDMS cylinders parallel to the trenches.

Additionally, a top PDMS wetting layer is present at the BCP surface because of its lower surface energy compared to PS. In Figure 3, this layer is not clearly evidenced, most likely because of a poor contrast between this Si-containing layer and the metallization layer.

Water contact angle measurements on PS-brush, PDMSbrush, and the BCP are emphasized though the presence of a PDMS surface layer. The water contact angles of PDMS- and PS-brush have been reported to be approximately 114 and 95° respectively. The as-spun BCP film and solvent vapor annealed film on planar SoC substrates were found to have a water contact angle of about 109 and 108°, respectively, indicating PDMS rich surface layers. Furthermore, it has been found that plasma etching requires a short CF<sub>4</sub> burst (withdrawal of the PDMS surface layer) to efficiently reveal and transfer the assembled PDMS lines.

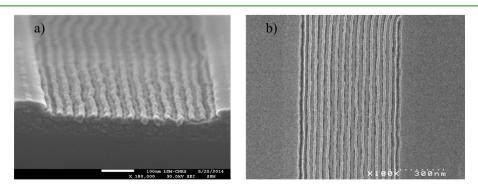

Examples of SEM cross-section and top-view of aligned horizontal PDMS cylinders within SiARC/SoC trenches are reported in Figure 4. Here, to visualize the pattern, short  $CF_4$ and HBr/O<sub>2</sub> plasma processes are used respectively to remove the PDMS surface layer and partially etch the PS matrix (The roughness observed between the PDMS lines is due to PS residues not yet completely etched during this transient state).

## 3. DRY ETCHING PROCESS OF THE DSA-BCP/SOC/SI STACK

Transferring the dense array of lines produced by DSA into the underlying substrate is particularly challenging with common plasma processes, due to the inherently high aspect ratio of the

Figure 4. (a) Cross-section and (b) top-view SEM images of directed self-assembled horizontal PDMS cylinders in the SiARC/SoC topographical template after 5 s CF<sub>4</sub> and 5 s HBr/O<sub>2</sub> plasma treatments.

16278

Figure 5. Schematic of the dry etching method used for the PS–PDMS/SoC/Si stack plasma processing. (a) CW HBr/O<sub>2</sub> plasma treatment to eliminate the PS matrix and transfer the pattern into the SoC layer, (b) Si transfer by pulsed HBr/O<sub>2</sub> plasma etching, (c) details of the induced charge distribution during step b.

15 nm lines. The stack is composed of a thin PDMS layer formed at the air/BCP interface, horizontal PDMS cylinders in a PS matrix, a SoC layer and the silicon substrate. Three etching steps are required for transferring the PDMS patterns into the silicon substrate: one to remove the PDMS layer at the top surface, a second one to etch at the same time the unprotected PS-matrix and the SoC layer and a third one to reproduce the pattern into the silicon substrate. Figure 5 illustrates these two last steps and the main chemical species involved.

**3.1. Lithographic Mask Formation.** Both the revelation (top PDMS wetting layer and PS matrix removal) and transfer of the PDMS lithographic mask in the SoC layer are realized in CW mode (step A and B in Table 1). First, the PDMS wetting

Table 1. Details of the Etching Process for PDMS Pattern

Transfer

| step <sup>a</sup> | etching<br>mode                   | pressure<br>(mTorr) | gas                                 | time (s) | bias<br>power<br>(W) | source<br>power<br>(W) |

|-------------------|-----------------------------------|---------------------|-------------------------------------|----------|----------------------|------------------------|

| А                 | CW                                | 4                   | CF <sub>4</sub> 100<br>sccm         | 5        | 20                   | 700                    |

| В                 | CW                                | 5                   | HBr/O <sub>2</sub><br>70/30<br>sccm | 5-25     | 120                  | 500                    |

| С                 | Pulsed<br>(Duty<br>cycle<br>=20%) | 20                  | HBr/O <sub>2</sub><br>200/5<br>sccm | 10-250   | 100                  | 750                    |

<sup>a</sup>Step A, PDMS wetting layer removal; step B, PS matrix and SoC layer etching; step C, transfer of the PDMS pattern into the silicon substrate.

layer at the air/BCP interface is removed by a 5 s CF<sub>4</sub> plasma (Step A). Then, the PS matrix of the BCP and the SoC layer are etched using a 25 s HBr/O<sub>2</sub> plasma (Step B). PS and SoC, being essentially composed of carbon, are removed with higher selectivity during this process step compared to PDMS. Indeed, oxygen radicals react with the carbon of the PS/SoC layer to form CO<sub>x</sub> volatile etch products. Furthermore, the introduction of bromine leads to the formation of weakly volatile etch products such as  $C_xH_yBr_z$  which can redeposit on the feature sidewalls and form a thin protection layer (pink walls on the schematic in Figure 5a). This passivation layer protects the sidewalls from lateral etching, allowing an excellent anisotropic etch of the lines. At the same time, the PDMS cylinders are

oxidized and transformed into a  $SiO_2$ -like material. Examples of samples obtained after this etching step are reported in Figure 6. High-aspect-ratio lines with vertical sidewalls are obtained.

3.2. Transfer Etching into the Silicon Substrate. The difficulty of etching high-aspect-ratio features lies in particular in the collection angle of the plasma neutrals (as seen from the trench bottom or sidewalls). The angle is restricted by shadowing the adjacent features, thus decreasing the passivation layer thickness on the sidewalls when increasing the aspect ratio. The lateral etching of features may then become important leading to a lift-off effect of the mask. Furthermore, insulating materials such as oxidized PDMS (and probably passivated SoC) are known to accumulate electric charges. As a consequence, the top of the feature sidewalls is negatively charged, and their bottom positively because the positive ions are directional, whereas the plasma electrons have an isotropic velocity distribution function.<sup>27</sup> As a result, the ions are slowed down and deviated toward the sidewalls. Figure 5c schematizes these phenomena. Consequently, at the bottom of a highaspect-ratio feature, the ion flux and energy is much lower than on planar substrates and etching can then stop or become too slow to ensure a reasonable etching depth with the available mask thickness. To overcome those issues, one possibility is to use pulsed plasmas. First, pulsing the plasma allows a precise control of the plasma chemistry,<sup>28</sup> and second, pulsed plasma tends to reduce or even eliminate charging of the features.<sup>29</sup> It also helps to overcome any charging by providing extremely energetic ions to the wafer compared to typical CW processes.24

In the pulsed plasma system used, the RF power delivered to the ICP coils is modulated ON and OFF periodically at 1 kHz (pulsing period of 1 ms) with a duty cycle of 20% (percentage of RF ON time). All the other parameters (gas flow, temperature, pressure, etc.) are kept constant with a baseline process composed of HBr/O<sub>2</sub> plasma with a low amount of oxygen (Table 1-Step C).

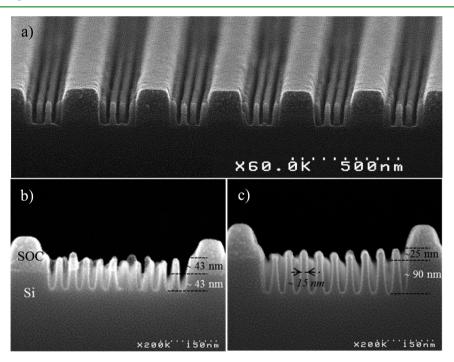

Figure 7 shows the etching profiles obtained after different plasma etching times. The 120 s process allows etching of about 43 nm deep silicon lines, whereas a 200 s process allows patterning 90 nm deep silicon lines. The averaged silicon etching rate is found to be  $\sim$ 0.4 nm/s with a Si/SoC etching selectivity of about 2.5 indicating that the mask is partially consumed during the process. Thus, a thick layer of SoC is necessary to maintain the pattern profile. J. However, the SoC

Figure 6. (a-c) Cross-section and (d) top-view SEM images of directed self-assembled horizontal PDMS cylinders transferred into a SoC layer after 5 s CF4 and 25 s HBr/O<sub>2</sub> plasma treatments.

Figure 7. Cross-section SEM images of the transfer etching in the silicon substrate of directed self-assembled horizontal PDMS cylinders using pulsed  $HBr/O_2$  plasma with (b) 120 s and (a, c) 200 s etching time.

layer is not entirely etched at the end of the silicon transfer etching process, a thin layer (25 nm) is still observed at the sample's surface after 200 s, protecting the upper part of the lines. The critical dimension (CD) of the lines is  $15 \pm 3$  nm, which corresponds to both PDMS cylinder and SoC line dimensions produced in the earlier etching steps. This indicates that a good CD control is performed using this process. It is important to underline that the CD control achieved in this process is due to the fact that the plasma is pulsed. Typical silicon etching processes in CW plasma fail to etch the silicon lines. The basic phenomena taking place during the two RF power phases can be explained as follows. During the ON phase, the plasma ignites and the electron (and ion) density rises to form  $H_2O^+$ ,  $O_2^+$ ,  $HBr^+$ ,  $Br_2^+$  reactive species.<sup>30,21</sup> The ions are accelerated to high energy (about 250 eV) by the self-

#### **ACS Applied Materials & Interfaces**

bias voltage that develops rapidly on the electrostatic chuck during this ON phase. Such a high energy allows the ions to reach the bottom of the trenches and assist in the etching process. Furthermore, the ion energy in pulsed plasma is high enough to sputter poorly volatile SiBr, species from the trench bottom. These species can redeposit on the feature sidewalls thus contributing importantly to their passivation.<sup>31</sup> In the ON period, electron dissociation reactions produce reactive radicals (O, Br, H, SiBrx) in the plasma which will stick on the sidewalls to form a protective SiOBr, passivation layer. However, it is well-known that due to shadowing effects, only the top of the high aspect ratio features can be protected by the passivation layer but not the bottom (oxygen atoms have a high sticking probability and cannot diffuse deep into the features).<sup>32</sup> The assistance of the SiBr species sputtered from the features bottom is expected to contribute significantly to form the sidewall passivation layers. The formed Sir,OyBr, layers allow the anisotropic etching profiles as shown in Figure 5 b).

During the OFF phase, the inductive electric field, responsible for the electron heating, vanishes rapidly and the electron temperature cools down in 10  $\mu$ s. Even though there is no production of radicals during this period, the radical density varies on time scales (several milliseconds) that are longer than the pulsing period (1 ms). Therefore, the radical density is only weakly modulated when the plasma is pulsed at 1 kHz or higher.<sup>22</sup> The plasma chemistry is controlled by the duty cycle (because radicals are produced in the ON period and lost in the OFF period) and the radical flux is the same in the OFF and ON periods. Hence, in the OFF period, radicals are participating to the passivation layer formation and enhance the Br coverage of the feature bottom. At the same time, the bias voltage drops rapidly to zero in the OFF period and the substrate is bombarded by very low energy ions. The low energy ions do not participate in the etching process but they are expected to be easily deflected by the negative charges accumulated on the mask and to neutralize them.

Pulsed plasma etching shows thus several benefits for high aspect ratio structure etching compared to continuous plasma etching. The particular chemical plasma composition, the bombardment of high energy ions in the ON period (which enhances etching and provides passivation) and low energy ions in the OFF period are expected to significantly improve the process.<sup>33</sup>

#### CONCLUSIONS AND PERSPECTIVES

We have generated periodic silicon line patterns by combining standard trilayer industry-type photolithography substrates with cylindrical high- $\chi$  BCP graphoepitaxy. Trenches realized in both the anti-reflective coating (SiARC) and the spin-on carbon (SoC) layers create guide lines for the directed self-assembly of the block copolymer. Horizontal cylinders were aligned within the trenches during solvent vapor annealing to form parallel features of PDMS in a PS matrix. Nanopatterns of oxidized PDMS were revealed by an HBr/O<sub>2</sub> plasma etch. Finally, the periodic patterns were transferred into the silicon substrate using dedicated pulsed plasma etching conditions. Silicon nanostructures with ~15 nm half-pitch line/space and a height up to 90 nm have been successfully obtained with a good control of the critical dimensions compared to the initial PDMS cylinder diameter. This process provides new opportunities for next-generation sub-10 nm lithography applications.

Further improvements and characterizations of the process are still ongoing. Concerning the SVA process, the work is dedicated to the decrease of the process time to a few minutes. First results show the importance of both the beginning and the end of the SVA process. A control of the swelling/deswelling rate in the annealing chamber would also be necessary to avoid the macroscopically observed dewetting defects. Controlling these defects is the key for an eventual integration of the PS-*b*-PDMS high- $\chi$  BCP into a microelectronics environment, and more generally onto large processing surfaces. On the other hand, more work is carried out on the measurement of the critical dimension uniformity (CDU) control during the whole etching process.

#### AUTHOR INFORMATION

#### **Corresponding Author**

\*E-mail: marc.zelsmann@cea.fr.

#### **Author Contributions**

The manuscript was written through contributions of all authors. All authors have given approval to the final version of the manuscript.

#### Funding

The research leading to these results has received funding from the European Union Seventh Framework Program (FP7/ 2007–2013) under LAMAND grant agreement 245565 and was partly supported by the French RENATECH network and by the French LabEx Minos ANR-10-LABX-55–01.

#### Notes

The authors declare no competing financial interest.

#### REFERENCES

(1) Namatsu, H.; Watanabe, Y.; Yamazaki, K.; Yamaguchi, T.; Nagase, M.; Ono, Y.; Fujiwara, a.; Horiguchi, S. Fabrication of Si Single-Electron Transistors with Precise Dimensions by Electron-Beam Nanolithography. *J. Vac. Sci. Technol., B* **2003**, *21*, 1.

(2) Hirai, Y.; Hafizovic, S.; Matsuzuka, N.; Korvink, J. G.; Tabata, O.; Member, S. Validation of X-Ray Lithography and Development Simulation System for Moving Mask Deep X-Ray Lithography. *J. Microelectromech. Syst.* **2006**, *15*, 159–168.

(3) Chou, S. Y. Nanoimprint Lithography. J. Vac. Sci. Technol., B 1996, 14, 4129.

(4) Dong, B.; Lu, N.; Zelsmann, M.; Kehagias, N.; Fuchs, H.; Sotomayor Torres, C. M.; Chi, L. F. Fabrication of High-Density, Large-Area Conducting-Polymer Nanostructures. *Adv. Funct. Mater.* **2006**, *16*, 1937–1942.

(5) Bang, J.; Jeong, U.; Ryu, D. Y.; Russell, T. P.; Hawker, C. J. Block Copolymer Nanolithography: Translation of Molecular Level Control to Nanoscale Patterns. *Adv. Mater.* **2009**, *21*, 4769–4792.

(6) Cheng, J. Y.; Ross, C. a.; Smith, H. I.; Thomas, E. L. Templated Self-Assembly of Block Copolymers: Top-Down Helps Bottom-Up. *Adv. Mater.* **2006**, *18*, 2505–2521.

(7) Jung, Y. S.; Ross, C. a. Orientation-Controlled Self-Assembled Nanolithography Using a Polystyrene-Polydimethylsiloxane Block Copolymer. *Nano Lett.* **2007**, *7*, 2046–2050.

(8) Li, H.-W.; Huck, W. T. S. Ordered Block-Copolymer Assembly Using Nanoimprint Lithography. *Nano Lett.* **2004**, *4*, 1633–1636.

(9) Campbell, I. P.; He, C.; Stoykovich, M. P. Topologically Distinct Lamellar Block Copolymer Morphologies Formed by Solvent and Thermal Annealing. *ACS Macro Lett.* **2013**, *2*, 918–923.

(10) Jeong, J. W.; Park, W. I.; Do, L.-M.; Park, J.-H.; Kim, T.-H.; Chae, G.; Jung, Y. S. Nanotransfer Printing with Sub-10 Nm Resolution Realized Using Directed Self-Assembly. *Adv. Mater.* **2012**, *24*, 3526–3531.

(11) Jung, Y. S.; Chang, J. B.; Verploegen, E.; Berggren, K. K.; Ross, C. a A Path to Ultranarrow Patterns Using Self-Assembled Lithography. *Nano Lett.* **2010**, *10*, 1000–1005.

#### **ACS Applied Materials & Interfaces**

(12) Park, W. I.; Kim, K.; Jang, H.-I.; Jeong, J. W.; Kim, J. M.; Choi, J.; Park, J. H.; Jung, Y. S. Directed Self-Assembly with Sub-100 Degrees Celsius Processing Temperature, Sub-10 Nanometer Resolution, and Sub-1 minute Assembly Time. *Small* **2012**, *8*, 3762–3768.

(13) ITRS. International Technology Roadmap for Semiconductors. 2013, http://www.itrs.net.

(14) Farrell, R. a; Fitzgerald, T. G.; Borah, D.; Holmes, J. D.; Morris, M. a. Chemical Interactions and Their Role in the Microphase Separation of Block Copolymer Thin Films. *Int. J. Mol. Sci.* **2009**, *10*, 3671–3712.

(15) Gotrik, K. W.; Ross, C. a. Solvothermal Annealing of Block Copolymer Thin Films. *Nano Lett.* **2013**, *13*, 5117–5122.

(16) Jung, Y. S.; Ross, C. a. Solvent-Vapor-Induced Tunability of Self-Assembled Block Copolymer Patterns. *Adv. Mater.* **2009**, *21*, 2540–2545.

(17) Chao, C.-C.; Ho, R.-M.; Georgopanos, P.; Avgeropoulos, A.; Thomas, E. L. Silicon Oxy Carbide Nanorings from Polystyrene-B-Polydimethylsiloxane Diblock Copolymer Thin Films. *Soft Matter* **2010**, *6*, 3582.

(18) Garra, J.; Long, T.; Currie, J.; Schneider, T.; White, R.; Paranjape, M. Dry Etching of Polydimethylsiloxane for Microfluidic Systems. J. Vac. Sci. Technol., A **2002**, 20, 975.

(19) Hartney, M. a.; Chiang, J. N.; Hess, D. W.; Soane, D. S. Oxide Formation during Plasma Etching of Silicon-Containing Resists. *Appl. Phys. Lett.* **1989**, *54*, 1510.

(20) Sinturel, C.; Vayer, M.; Morris, M.; Hillmyer, M. a. Solvent Vapor Annealing of Block Polymer Thin Films. *Macromolecules* **2013**, *46*, 5399–5415.

(21) Petit-Etienne, C.; Darnon, M.; Vallier, L.; Pargon, E.; Cunge, G.; Boulard, F.; Joubert, O.; Banna, S.; Lill, T. Reducing Damage to Si Substrates during Gate Etching Processes by Synchronous Plasma Pulsing. J. Vac. Sci. Technol., B **2010**, 28, 926.

(22) Cunge, G.; Bodart, P.; Brihoum, M.; Boulard, F.; Chevolleau, T.; Sadeghi, N. Ion Flux and Ion Distribution Function Measurements in Synchronously Pulsed Inductively Coupled Plasmas. *J. Vac. Sci. Technol., A* **2012**, *31*, 020604.

(23) Cunge, G.; Vempaire, D.; Ramos, R.; Touzeau, M.; Joubert, O.; Bodard, P.; Sadeghi, N. Radical Surface Interactions in Industrial Silicon Plasma Etch Reactors. *Plasma Sources Sci. Technol.* **2010**, *19*, 34017.

(24) Brihoum, M.; Cunge, G.; Darnon, M.; Gahan, D.; Joubert, O.; Braithwaite, N. S. J. Ion Flux and Ion Distribution Function Measurements in Synchronously Pulsed Inductively Coupled Plasmas. J. Vac. Sci. Technol., A 2013, 31, 020604.

(25) Salaun, M.; Zelsmann, M.; Archambault, S.; Borah, D.; Kehagias, N.; Simao, C.; Lorret, O.; Shaw, M. T.; Sotomayor Torres, C. M.; Morris, M. a. Fabrication of Highly Ordered Sub-20 Nm Silicon Nanopillars by Block Copolymer Lithography Combined with Resist Design. J. Mater. Chem. C 2013, 1, 3544.

(26) O'Driscoll, B. M. D.; Kelly, R. a.; Shaw, M.; Mokarian-Tabari, P.; Liontos, G.; Ntetsikas, K.; Avgeropoulos, A.; Petkov, N.; Morris, M. a. Achieving Structural Control with Thin Polystyrene-B-Polydimethylsiloxane Block Copolymer Films: The Complex Relationship of Interface Chemistry, Annealing Methodology and Process Conditions. *Eur. Polym. J.* 2013, 49, 3445–3454.

(27) Hwang, G. S.; Giapis, K. P. On the Origin of the Notching Effect during Etching in Uniform High Density Plasmas. J. Vac. Sci. Technol., B 1997, 15, 70.

(28) Bodart, P.; Brihoum, M.; Cunge, G.; Joubert, O.; Sadeghi, N. Analysis of Pulsed High-Density HBr and Cl2 Plasmas: Impact of the Pulsing Parameters on the Radical Densities. *J. Appl. Phys.* **2011**, *110*, 113302.

(29) Giapis, K. P.; Hwang, G. S. Pattern-Dependent Charging and the Role of Electron Tunneling. *Jpn. J. Appl. Phys.* **1998**, *37*, 2291.

(30) Darnon, M.; Petit-Etienne, C.; Pargon, E.; Cunge, G.; Vallier, L.; Bodart, P.; Haas, M.; Banna, S.; Lill, T.; Joubert, O. Synchronous Pulsed Plasma for Silicon Etch Applications. *ECS Trans.* **2010**, *27*, 717–723. (31) Luere, O.; Pargon, E.; Vallier, L.; Pelissier, B.; Joubert, O. Etch Mechanisms of Silicon Gate Structures Patterned in SF[sub 6]/ CH[sub 2]F[sub 2]/Ar Inductively Coupled Plasmas. J. Vac. Sci. Technol., B. 2011, 29, 011028.

(32) Detter, X.; Palla, R.; Thomas-Boutherin, I.; Pargon, E.; Cunge, G.; Joubert, O.; Vallier, L. Impact of Chemistry on Profile Control of Resist Masked Silicon Gates Etched in High Density Halogen-Based Plasmas. J. Vac. Sci. Technol., B 2003, 21, 2174.

(33) Banna, S.; Agarwal, A.; Cunge, G.; Darnon, M.; Pargon, E.; Joubert, O. Pulsed High-Density Plasmas for Advanced Dry Etching Processes. J. Vac. Sci. Technol., A **2012**, 30, 040801.